# ACE: An Authenticated Encryption and Hash Algorithm

# Submission to the NIST LWC Competition

SUBMITTERS/DESIGNERS: Mark Aagaard, Riham AlTawy<sup>1</sup>, Guang Gong, Kalikinkar Mandal, and Raghvendra Rohit<sup>\*</sup>

> \*Corresponding submitter: Email: rsrohit@uwaterloo.ca Tel: +1-519-888-4567 x45650

COMMUNICATION SECURITY LAB Department of Electrical and Computer Engineering University of Waterloo 200 University Avenue West Waterloo, ON, N2L 3G1, CANADA

https://uwaterloo.ca/communications-security-lab/lwc/ace

September 27, 2019

<sup>&</sup>lt;sup>1</sup>Currently with Department of Electrical and Computer Engineering, University of Victoria, 3800 Finnerty Rd, Victoria, BC, V8P 5C2, CANADA

# Contents

| 1 | Intr | oduction                               | <b>7</b>  |

|---|------|----------------------------------------|-----------|

|   | 1.1  | Notations                              | 8         |

|   | 1.2  | Outline                                | 9         |

| 2 | Spe  | ification                              | 10        |

|   | 2.1  | Parameters                             | 10        |

|   |      | 2.1.1 ACE AEAD algorithm               | 10        |

|   |      | 2.1.2 ACE Hash algorithm               | 11        |

|   | 2.2  | Recommended Parameter Set              | 11        |

|   | 2.3  | The ACE Permutation                    | 11        |

|   |      | 2.3.1 The nonlinear function SB-64     | 11        |

|   |      | 2.3.2 Round and step constants         | 12        |

|   | 2.4  | AEAD Algorithm: $ACE-\mathcal{AE}-128$ | 14        |

|   |      | 2.4.1 Rate and capacity part of state  | 15        |

|   |      | 2.4.2 Padding                          | 15        |

|   |      | 2.4.3 Loading key and nonce            | 16        |

|   |      | 2.4.4 Initialization                   | 16        |

|   |      | 2.4.5 Processing associated data       | 16        |

|   |      | 2.4.6 Encryption                       | 16        |

|   |      | 2.4.7 Finalization                     | 17        |

|   |      | 2.4.8 Decryption                       | 17        |

|   | 2.5  | Hash Algorithm: ACE-H-256              | 17        |

|   |      | 2.5.1 Message padding                  | 18        |

|   |      | 2.5.2 Loading initialization vector    | 18        |

|   |      | 2.5.3 Initialization                   | 18        |

|   |      | 2.5.4 Absorbing and squeezing          | 18        |

| 3 | Secu | rity Claims                            | 20        |

| 4 | Secu | rity Analysis                          | <b>21</b> |

|   | 4.1  | Diffusion                              | 21        |

|   | 4.2  | Differential and Linear Cryptanalysis  | 21        |

|   |       | 4.2.1 Expected bounds on the maximum probabilities of differential |           |

|---|-------|--------------------------------------------------------------------|-----------|

|   |       |                                                                    | 22        |

|   | 4.3   | Algebraic Properties                                               | 22        |

|   | 4.4   |                                                                    | 24        |

|   | 4.5   | Security of ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256   | 25        |

| 5 | Des   | ign Rationale 2                                                    | 26        |

|   | 5.1   | Choice of the Mode: sLiSCP Sponge Mode                             | 26        |

|   | 5.2   |                                                                    | 27        |

|   | 5.3   |                                                                    | 28        |

|   | 5.4   |                                                                    | 28        |

|   | 5.5   |                                                                    | 29        |

|   | 5.6   |                                                                    | 29        |

|   |       | 5.6.1 Rationale                                                    | 29        |

|   |       | 5.6.2 Generation of round and step constants                       | 29        |

|   | 5.7   | Number of Rounds and Steps                                         | 31        |

|   | 5.8   | Choice of Rate Positions                                           | 32        |

|   | 5.9   |                                                                    | 32        |

| 0 |       |                                                                    |           |

| 6 |       | 8                                                                  | 33        |

|   | 6.1   |                                                                    | 33        |

|   | 6.2   | 1                                                                  | 34        |

|   |       | 1                                                                  | 35        |

|   |       |                                                                    | 37<br>40  |

|   | 6.9   | 1                                                                  |           |

|   | 6.3   | 1                                                                  | 42<br>49  |

|   |       |                                                                    | 42        |

|   | C A   | 1                                                                  | 47<br>5 1 |

|   | 6.4   | 1                                                                  | 51        |

|   |       |                                                                    | 52        |

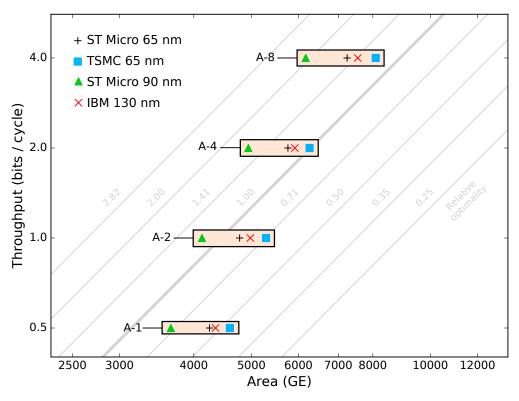

|   |       | 6.4.2 Implementation results                                       | 52        |

| 7 | Effic |                                                                    | 55        |

|   | 7.1   | 0 1                                                                | 55        |

|   | 7.2   | Software: Microcontroller                                          | 58        |

| Α | Oth   | er NIST-LWC Submissions 6                                          | 64        |

| В | Test  | Vectors                                                            | 35        |

|   | B.1   |                                                                    | 35        |

|   | B.2   |                                                                    | 56        |

|   | B.3   |                                                                    | 56        |

|   |       |                                                                    | 56        |

|   |       |                                                                    | -         |

# C Constants: Sequence to Hex Conversion

# List of Figures

| 2.1  | ACE-step                                                                   | 12 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | Simeck sbox (SB-64)                                                        | 12 |

| 2.3  | Schematic diagram of ACE- $\mathcal{AE}$ -128 AEAD algorithm               | 15 |

| 2.4  | Hash algorithm ACE- $\mathcal{H}$ -256                                     | 18 |

| 5.1  | LFSR for generating ACE constants                                          | 30 |

| 5.2  | Schematic of the 3-way parallel LFSR for generation of the constants .     | 30 |

| 5.3  | Generation of three 8-bit step constants                                   | 31 |

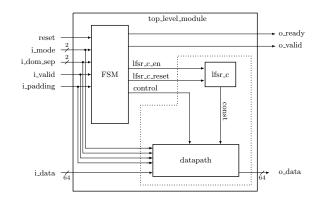

| 6.1  | Top-level ACE_module and the interface with the environment $\ldots$       | 35 |

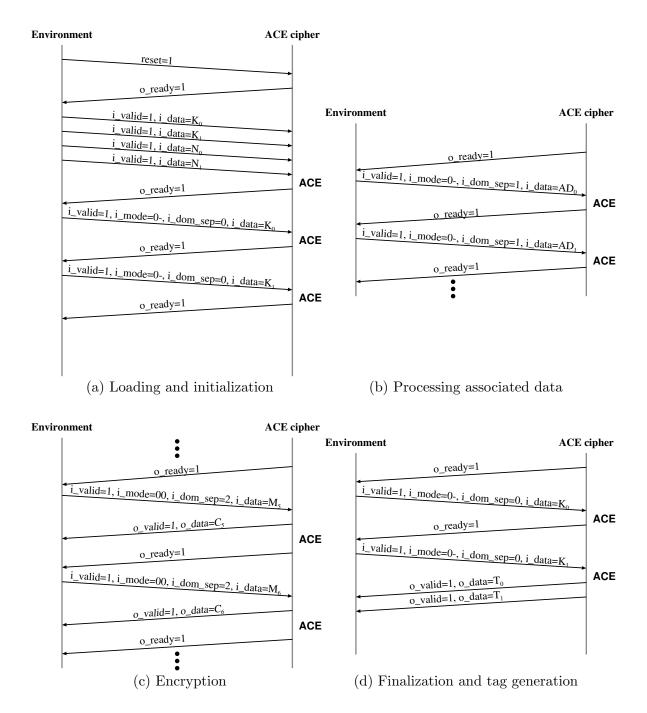

| 6.2  | Interface protocol                                                         | 36 |

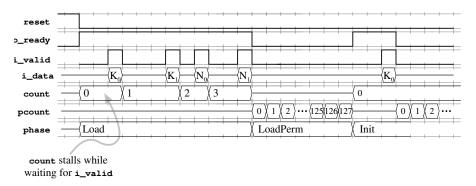

| 6.3  | Timing diagram: Loading and initialization during ACE- $\mathcal{AE}$ -128 | 38 |

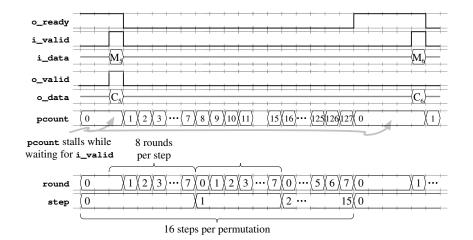

| 6.4  | Timing diagram: Encryption during ACE- $\mathcal{AE}$ -128                 | 39 |

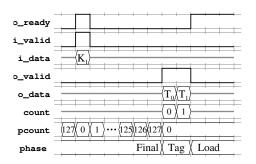

| 6.5  | Timing of tag phase during ACE- $\mathcal{AE}$ -128                        | 39 |

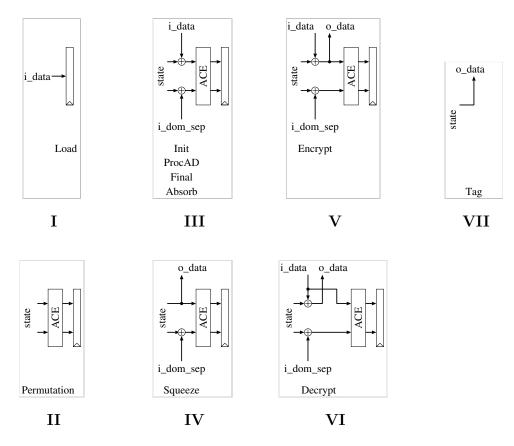

| 6.6  | Phases and datapath operations                                             | 41 |

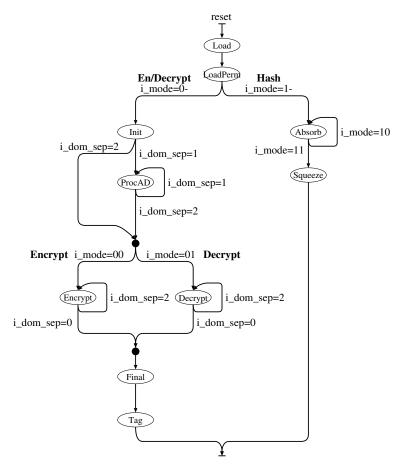

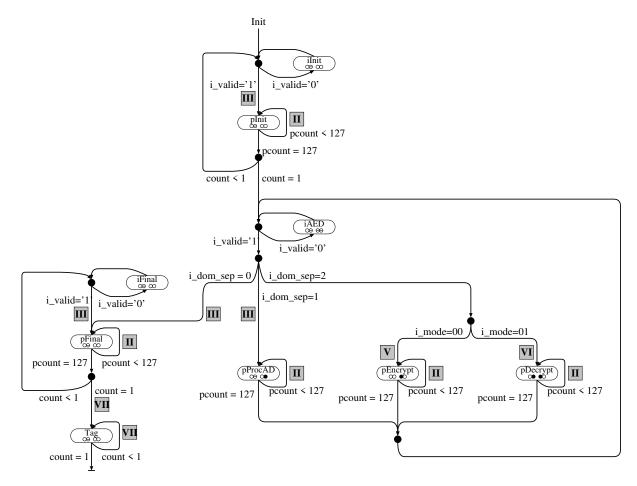

| 6.7  | Control flow between phases                                                | 43 |

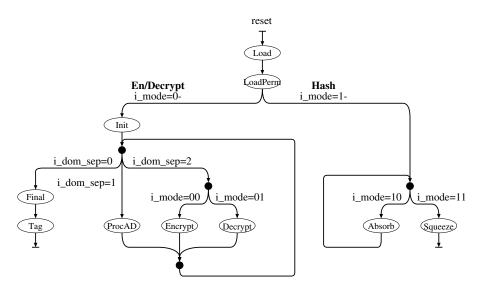

| 6.8  | Optimized control flow between phases                                      | 43 |

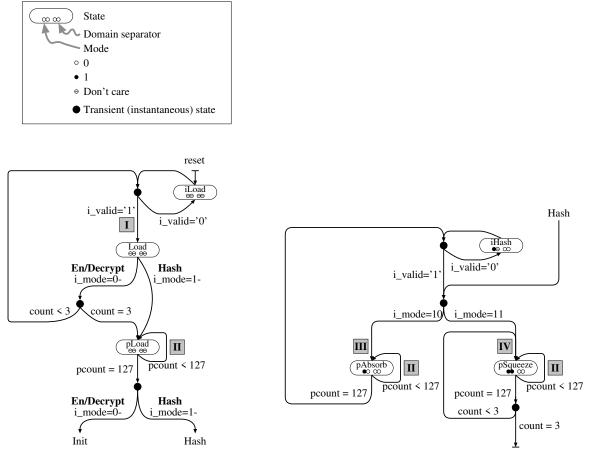

| 6.9  | State machine: Loading                                                     | 46 |

| 6.10 | State machine: Hashing                                                     | 46 |

| 6.11 | State machine: Encryption and decryption                                   | 47 |

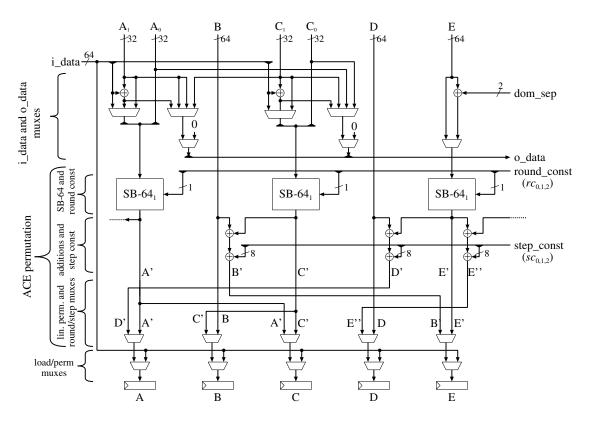

| 6.12 | The ACE-datapath                                                           | 48 |

| 6.13 | Area <sup>2</sup> vs Throughput                                            | 53 |

|      |                                                                            |    |

# List of Tables

| $2.1 \\ 2.2$                                                                                       | Recommended parameter set for ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256 Round and step constants of ACE                   | 11<br>13                                           |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| $3.1 \\ 3.2$                                                                                       | Security goals of ACE- $\mathcal{AE}$ -128 (in bits)                                                                                 | 20<br>20                                           |

| $4.1 \\ 4.2 \\ 4.3$                                                                                | Minimum number of active Simeck sboxes for s-step ACEACEBounds on the algebraic degree of ACEIntegral distinguishers of ACE          | 23<br>24<br>24                                     |

| 5.1                                                                                                | MEDCP of ACE for $s = 15, 16$                                                                                                        | 32                                                 |

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \end{array}$ | Interface signals                                                                                                                    | 34<br>34<br>42<br>50<br>50<br>51<br>52<br>53<br>54 |

| 7.1<br>7.2                                                                                         | Benchmarking the results for the ACE permutation and its modes Performance of ACE on microcontrollers at a clock frequency of 16 MHz | $58 \\ 59$                                         |

| A.1                                                                                                | Submissions with sLISCP-light like permutations                                                                                      | 64                                                 |

| B.1                                                                                                | Test vector for ACE permutation                                                                                                      | 66                                                 |

| C.1                                                                                                | Generation of round and step constants for $i = 0 \dots \dots \dots \dots \dots$                                                     | 68                                                 |

# Chapter 1 Introduction

ACE, often known as one of the strongest cards in a deck of cards, is a 320-bit lightweight permutation. It is designed to achieve a balance between hardware cost and software efficiency for both Authenticated Encryption with Associated Data (henceforth "AEAD") and hashing functionalities, while providing sufficient security margins. To accomplish these goals, ACE components and its mode of operation are adopted from well known and analyzed cryptographic primitives. In a nutshell, the design of ACE, its security, functionalities and the features it offers are described as follows.

- ACE core operations. Bitwise XORs and ANDs, left cyclic shifts and 64-bit word shuffles

- ACE nonlinear layer. Unkeyed round-reduced Simeck block cipher [30] with blocksize of 64-bits, which provides good cryptographic properties and low hardware cost

- ACE linear layer. Five 64-bit words are shuffled in an (3, 2, 0, 4, 1) order, which offers good resistance against differential and linear cryptanalysis

- ACE security. Simple analysis and security bounds provided using automated tools such as CryptoSMT solver [25] and Gurobi [1]

- Functionality. All-in-one primitive, provides both AEAD and hashing functionalities using the same hardware circuit

- ACE mode of operation. Unified sponge duplex mode [5]

- Security of ACE modes. 128-bit security

- Hardware performance. Efficient in hardware. Achieves a throughput of 360 Mbps and has an area of 4250 GE in a 65 nm ASIC. Implementation results are presented for four ASIC libraries and two FPGAs along with parallel implementations.

- Software performance. Bit-sliced implementation of ACE permutation achieves a speed of 9.97 cycles/byte

| Notation                                                                 | Description                                                                                                                         |  |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| $\overline{X \odot Y, X \oplus Y, X    Y}$                               | bitwise AND, XOR and concatenation of $X$ and $Y$                                                                                   |  |  |  |  |

| X                                                                        | length of $X$ in bits                                                                                                               |  |  |  |  |

| $\{0,1\}^n,\{0,1\}^\star,\phi$                                           | length $n$ bitstring, variable length bitstring, empty string                                                                       |  |  |  |  |

| $1^{n}, 0^{n}$                                                           | length $n$ bitstring with all 1's, 0's                                                                                              |  |  |  |  |

| Li                                                                       | left cyclic shift operator, i.e., for $x \in \{0, 1\}^n$ ,<br>$L^{i}(x) = (x_i, x_{i+1}, \dots, x_{n-1}, x_0, x_1, \dots, x_{i-1})$ |  |  |  |  |

| word/block                                                               | a 64-bit binary string                                                                                                              |  |  |  |  |

| S                                                                        | 320 bit state of ACE                                                                                                                |  |  |  |  |

| $S_r, S_c$                                                               | <i>r</i> -bit rate part and <i>c</i> -bit capacity part of $S$ ( $r = 64, c = 256$ )                                                |  |  |  |  |

| A, B, C, D, E                                                            | five 64-bit words of S, i.e., $S = A  B  C  D  E$                                                                                   |  |  |  |  |

| $S^i$                                                                    | state at <i>i</i> -th iteration (also step) of $ACE$ permutation                                                                    |  |  |  |  |

| A[j]                                                                     | j-th byte of word A starting from right                                                                                             |  |  |  |  |

| $A_1^i, A_0^i$                                                           | right and left half of word $A^i$                                                                                                   |  |  |  |  |

| $\overline{K, N, T}$                                                     | key, nonce and tag                                                                                                                  |  |  |  |  |

| k, n, t                                                                  | length of key, nonce and tag in bits $(k = n = t = 128)$                                                                            |  |  |  |  |

| AD, M, C                                                                 | associated data, plaintext and ciphertext (in blocks $AD_i, M_i, C_i$                                                               |  |  |  |  |

| <i>IV</i> , <i>iv</i> fixed initialization vector and its length in bits |                                                                                                                                     |  |  |  |  |

| H,h                                                                      | message digest (in blocks $H_i$ ) and its length $h = 256$                                                                          |  |  |  |  |

| $\ell_X$                                                                 | length of X in words where $X \in \{AD, M, C\}$                                                                                     |  |  |  |  |

| step                                                                     | one round of ACE permutation (see Figure $2.1$ )                                                                                    |  |  |  |  |

| round                                                                    | one round of Simeck unkeyed function (see Figure $2.2$ )                                                                            |  |  |  |  |

| SB-64                                                                    | nonlinear operation of $ACE$ permutation                                                                                            |  |  |  |  |

| u                                                                        | number of rounds, $u = 8$                                                                                                           |  |  |  |  |

| s                                                                        | number of steps, $s = 16$                                                                                                           |  |  |  |  |

| $rc_0^i, rc_1^i, rc_2^i$                                                 | 8-bit round constants                                                                                                               |  |  |  |  |

| $sc_0^i, sc_1^i, sc_2^i$                                                 | 8-bit step constants                                                                                                                |  |  |  |  |

| $\overline{ACE\text{-}\mathcal{AE}\text{-}k}$                            | ACE AEAD algorithm $(k = 128)$                                                                                                      |  |  |  |  |

| $ACE\text{-}\mathcal{H}\text{-}h$                                        | ACE Hash algorithm $(h = 256)$                                                                                                      |  |  |  |  |

# 1.1 Notations

# 1.2 Outline

The rest of the document is organized as follows. In Chapter 2, we present the complete specification of the ACE permutation, ACE AEAD and ACE hash algrithms. We summarize the security claims of our submission in Chapter 3 and provide the detailed security analysi in Chapter 4. In Chapter 5, we present the rationale behind our design and justify the parameter choices. The details of our hardware implementations and performance results in ASIC and FPGA are provided in Chapter 6. In Chapter 7, we discuss the efficiency of ACE in software including bit-sliced and microcontroller implementations. Finally, we conclude with references and test vectors in Appendix B.

# Chapter 2 Specification

### 2.1 Parameters

ACE is a 320-bit permutation that operates in a unified duplex sponge mode [5] and offers both AEAD and hashing functionalities in a single hardware circuit. The AEAD algorithm (ACE- $\mathcal{AE}$ -k) and the hash algorithm (ACE- $\mathcal{H}$ -h) are parameterized by the size k of the secret key and the length of the message digest h in bits, respectively. Both the algorithms process the same amount of data per permutation call (i.e., rate r is same) and hence r value is ignored in the individual parameters' description.

#### 2.1.1 **ACE** AEAD algorithm

The AEAD algorithm ACE- $\mathcal{AE}$ -k is a combination of two algorithms, an authenticated encryption algorithm ACE- $\mathcal{E}$  and the verified decryption algorithm ACE- $\mathcal{D}$ .

An authenticated encryption algorithm ACE- $\mathcal{E}$  takes as input a secret key K of length k bits, a public message number N (nonce) of size n bits, a block header AD (a.k.a, associated data) and a message M. The output of ACE- $\mathcal{E}$  is an authenticated ciphertext C of same length as M, and an authentication tag T of size t bits. Mathematically, ACE- $\mathcal{E}$  is defined as

$$\mathsf{ACE-}\mathcal{E}: \{0,1\}^k \times \{0,1\}^n \times \{0,1\}^* \times \{0,1\}^* \to \{0,1\}^* \times \{0,1\}^t$$

with

$$\mathsf{ACE}\text{-}\mathcal{E}(K, N, AD, M) = (C, T).$$

The decryption and verification algorithm takes as input the secret key K, nonce N, associated data AD, ciphertext C and tag T, and outputs the plaintext M of same length as C only if the verification of tag is correct, and  $\perp$  (error symbol) if the tag verification fails. More formally,

$$\mathsf{ACE-}\mathcal{D}(K, N, AD, C, T) \in \{M, \bot\}.$$

#### 2.1.2 **ACE** Hash algorithm

A hash algorithm takes message M and a pre-defined initialization vector IV of length iv bits as inputs, and returns a fixed size output H, called hash or message digest. Formally, the hash algorithm using ACE permutation is specified by

ACE-

$$\mathcal{H}$$

-h:  $\{0,1\}^* \times \{0,1\}^{iv} \to \{0,1\}^h$

with  $H = \mathsf{ACE-}\mathcal{H}-h(M, IV)$ .

Note that IV and N refer to two different things. IV is for a hash function and is fixed, while N is for an AEAD algorithm and never repeated for a fixed key.

### 2.2 Recommended Parameter Set

In Table 2.1, we list the recommended parameter set for the AEAD and hash fuctionalities using the ACE permutation. The length of each parameter is given in bits and ddenotes the amount of allowed data (including both AD and M) before a re-keying is required.

Table 2.1: Recommended parameter set for ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256

| Functionality | Algorithm                | r  | k   | n   | t   | $\log_2(d)$ | h   | iv |

|---------------|--------------------------|----|-----|-----|-----|-------------|-----|----|

| AEAD          | ACE- $\mathcal{AE}$ -128 | 64 | 128 | 128 | 128 | 124         | -   | -  |

| Hash          | ACE- <i>H</i> -256       | 64 | -   | -   | -   | -           | 256 | 24 |

### 2.3 The ACE Permutation

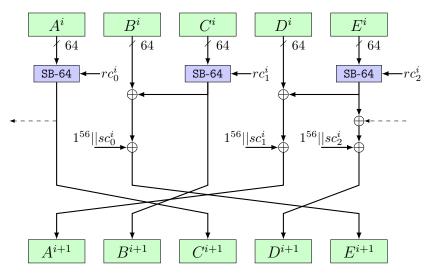

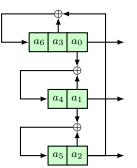

ACE is an iterative permutation that takes a 320-bit state as an input and outputs a 320-bit state after iterating the step function ACE-step for s = 16 times (Figure 2.1). The nonlinear operation SB-64 is applied on even indexed words (i.e., A, C and E, see Figure 2.1) and hence the permutation name. We present the algorithmic description of ACE in Algorithm 1.

#### 2.3.1 The nonlinear function SB-64

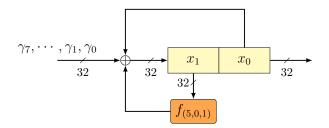

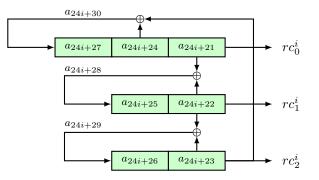

In ACE, we use unkeyed reduced-round Simeck block cipher [30] with block size 64 and u = 8 as the nonlinear operation, and denote it by SB-64. Below we provide the details of SB-64, henceforth referred to as Simeck sbox.

Figure 2.1: ACE-step

**Definition 1 (SB-64: Simeck sbox** [5]) Let  $rc = (q_7, q_6, \ldots, q_0)$  where  $q_j \in \{0, 1\}$ and  $0 \le j \le 7$ . A Simeck sbox is a permutation of a 64-bit input, constructed by iterating the Simeck-64 block cipher for 8 rounds with round constant addition  $\gamma_j = 1^{31} ||q_j|$ in place of key addition.

Figure 2.2: Simeck sbox (SB-64)

An illustrated description of the Simeck sbox is shown in Figure 2.2 and is given by

$$(x_9||x_8) \leftarrow \text{SB-64}(x_1||x_0, rc)$$

where

$$x_j \leftarrow f_{(5,0,1)}(x_{j-1}) \oplus x_{j-2} \oplus \gamma_{j-2}, \ 2 \le j \le 9$$

and  $f_{(5,0,1)}: \{0,1\}^{32} \to \{0,1\}^{32}$  is defined as

$$f_{(5,0,1)}(x) = (\mathsf{L}^{5}(x) \odot x) \oplus \mathsf{L}^{1}(x).$$

#### 2.3.2 Round and step constants

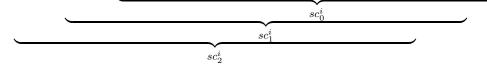

The step function of ACE is parameterized by two sets of triplets  $(rc_0^i, rc_1^i, rc_2^i)$  and  $(sc_0^i, sc_1^i, sc_2^i)$  where each  $rc_j^i$  and  $sc_j^i$  is of length 8 bits and j = 0, 1, 2. We call them

Algorithm 1 ACE permutation

```

1: Input: S^0 = A^0 ||B^0||C^0||D^0||E^0|

2: Output: S^{16} = A^{16} ||B^{16}||C^{16}||D^{16}||E^{16}|

3: for i = 0 to 15 do:

S^{i+1} \leftarrow \mathsf{ACE-step}(S^i)

4:

5: return S^{16}

6: Function ACE-step(S^i):

A^i \leftarrow \text{SB-64}(A_1^i || A_0^i, rc_0^i)

7:

C^i \leftarrow \text{SB-64}(C_1^i || C_0^i, rc_1^i)

8:

E^i \leftarrow \text{SB-64}(E_1^i || E_0^i, rc_2^i)

9:

B^i \leftarrow B^i \oplus C^i \oplus (1^{56} || sc_0^i)

10:

D^i \leftarrow D^i \oplus E^i \oplus (1^{56} || sc_1^i)

11:

E^i \leftarrow E^i \oplus A^i \oplus (1^{56} || sc_2^i)

12:

A^{i+1} \leftarrow D^i

13:

B^{i+1} \leftarrow C^i

14:

C^{i+1} \leftarrow A^i

15:

D^{i+1} \leftarrow E^i

16:

E^{i+1} \leftarrow B^i

17:

return (A^{i+1}||B^{i+1}||C^{i+1}||D^{i+1}||E^{i+1})

18:

19: Function SB-64(x_1||x_0, rc):

rc = (q_7, q_6, \ldots, q_0)

20:

for j = 2 to 9 do

21:

x_{i} \leftarrow (\mathsf{L}^{5}(x_{i-1}) \odot x_{i-1}) \oplus \mathsf{L}^{1}(x_{i-1}) \oplus x_{i-2} \oplus (1^{31} || q_{i-2})

22:

23:

return (x_9||x_8)

```

round constants and step constants, respectively. As shown in Figure 2.1, the round constant triplet  $(rc_0^i, rc_1^i, rc_2^i)$  is used within the Simeck sboxes while the step constant  $(sc_0^i, sc_1^i, sc_2^i)$  is XORed to the words B, D and E.

In Table 2.2 we list the hexadecimal values of the constants and show the procedure to generate these constants in Section 5.6.2.

| Step $i$ | <b>Round constants</b> $(rc_0^i, rc_1^i, rc_2^i)$      | <b>Step constants</b> $(sc_0^i, sc_1^i, sc_2^i)$       |

|----------|--------------------------------------------------------|--------------------------------------------------------|

| 0 - 3    | (07, 53, 43), (0a, 5d, e4), (9b, 49, 5e), (e0, 7f, cc) | (50, 28, 14), (5c, ae, 57), (91, 48, 24), (8d, c6, 63) |

| 4 - 7    | (d1, be, 32), (1a, 1d, 4e), (22, 28, 75), (f7, 6c, 25) | (53, a9, 54), (60, 30, 18), (68, 34, 9a), (e1, 70, 38) |

| 8 - 11   | (62, 82, fd), (96, 47, f9), (71, 6b, 76), (aa, 88, a0) | (f6, 7b, bd), (9d, ce, 67), (40, 20, 10), (4f, 27, 13) |

| 12 - 15  | (2b, dc, b0), (e9, 8b, 09), (cf, 59, 1e), (b7, c6, ad) | (be, 5f, 2f), (5b, ad, d6), (e9, 74, ba), (7f, 3f, 1f) |

Table 2.2: Round and step constants of ACE

# 2.4 AEAD Algorithm: ACE-AE-128

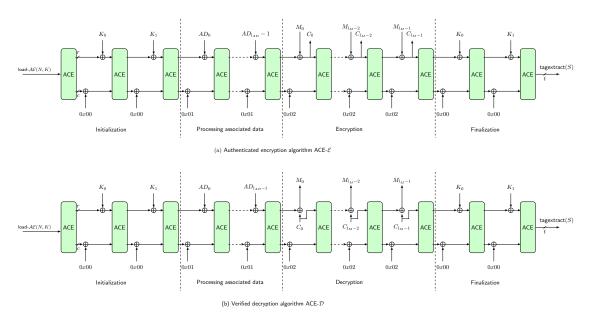

In Algorithm 2, we present a high-level overview of ACE- $\mathcal{AE}$ -128. The encryption (ACE- $\mathcal{E}$ ) and decryption (ACE- $\mathcal{D}$ ) processes of ACE- $\mathcal{AE}$ -128 are shown in Figure 2.3. In what follows, we first illustrate the position of rate and capacity bytes of the state, and the padding rule. We then describe each phase of ACE- $\mathcal{E}$  and ACE- $\mathcal{D}$ .

| Alg   | orithm 2 ACE- $\mathcal{AE}$ -128 algorithm                      |       |                                                                                                            |

|-------|------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------|

| 1: A  | uthenticated encryption ACE- $\mathcal{E}(K, N, AD, M)$ :        | 1: V  | /erified decryption ACE- $\mathcal{D}(K, N, AD, C, T)$ :                                                   |

| 2:    | $S \leftarrow Initialization(N,K)$                               | 2:    | $S \leftarrow Initialization(N, K)$                                                                        |

| 3:    | if $ AD  \neq 0$ then:                                           | 3:    | if $ AD  \neq 0$ then:                                                                                     |

| 4:    | $S \leftarrow Processing-Associated-Data(S, AD)$                 | 4:    | $S \leftarrow Processing\operatorname{-Associated}\operatorname{\!-Data}(S,AD)$                            |

| 5:    | $(S,C) \leftarrow Encyption(S,M)$                                | 5:    | $(S, M) \leftarrow Decyption(S, C)$                                                                        |

| 6:    | $T \leftarrow Finalization(S, K)$                                | 6:    | $T' \leftarrow Finalization(S, K)$                                                                         |

| 7:    | $\mathbf{return}\ (C,T)$                                         | 7:    | if $T' \neq T$ then:                                                                                       |

|       |                                                                  | 8:    | $\mathbf{return} \perp$                                                                                    |

| 8: Ir | itialization $(N, K)$ :                                          | 9:    | else:                                                                                                      |

| 9:    | $S \leftarrow load\text{-}\mathcal{AE}(N,K)$                     | 10:   | $\mathbf{return} \ M$                                                                                      |

| 10:   | $S \leftarrow ACE(S)$                                            |       |                                                                                                            |

| 11:   | for $i = 0$ to 1 do:                                             | 11: 1 | Decryption(S,C):                                                                                           |

| 12:   | $S \leftarrow (S_r \oplus K_i, S_c)$                             | 12:   | $(C_0  \cdots  C_{\ell_C-1}) \leftarrow pad_r(C)$                                                          |

| 13:   | $S \leftarrow ACE(S)$                                            | 13:   | for $i = 0$ to $\ell_C - 2$ do:                                                                            |

| 14:   | return S                                                         | 14:   | $M_i \leftarrow C_i \oplus S_r$                                                                            |

|       |                                                                  | 15:   | $S \leftarrow (C_i, S_c \oplus 0^{c-2}    10)$                                                             |

| 15: F | $\label{eq:processing-Associated-Data} (S, AD):$                 | 16:   | $S \leftarrow ACE(S)$                                                                                      |

| 16:   | $(AD_0  \cdots  AD_{\ell_{AD}-1}) \leftarrow pad_r(AD)$          | 17:   | $M_{\ell_C - 1} \leftarrow S_r \oplus C_{\ell_C - 1}$                                                      |

| 17:   | for $i = 0$ to $\ell_{AD} - 1$ do:                               | 18:   | $C_{\ell_C-1} \leftarrow trunc-msb(C_{\ell_C-1},  C  \bmod r)   trunc-lsb(M_{\ell_C-1}, r -  C  \bmod r) $ |

| 18:   | $S \leftarrow (S_r \oplus AD_i, S_c \oplus 0^{c-2}    01)$       | 19:   | $M_{\ell_C - 1} \leftarrow trunc-msb(M_{\ell_C - 1},  C  \bmod r)$                                         |

| 19:   | $S \leftarrow ACE(S)$                                            | 20:   | $M \leftarrow (M_0, M_1, \dots, M_{\ell_C - 1})$                                                           |

| 20:   | return $S$                                                       | 21:   | $S \leftarrow ACE(C_{\ell_C - 1}, S_c \oplus 0^{c - 2}    10)$                                             |

|       |                                                                  | 22:   | $\mathbf{return}\ (S,M)$                                                                                   |

| 21: E | Encryption $(S, M)$ :                                            |       |                                                                                                            |

| 22:   | $(M_0  \cdots  M_{\ell_M-1}) \gets pad_r(M)$                     | 23: F | Finalization $(S, K)$ :                                                                                    |

| 23:   | for $i = 0$ to $\ell_M - 1$ do:                                  | 24:   | for $i = 0$ to 1 do:                                                                                       |

| 24:   | $C_i \leftarrow M_i \oplus S_r$                                  | 25:   | $S \leftarrow ACE(S_r \oplus K_i, S_c)$                                                                    |

| 25:   | $S \leftarrow (C_i, S_c \oplus 0^{c-2}    10)$                   | 26:   | $T \gets tagextract(S)$                                                                                    |

| 26:   | $S \leftarrow ACE(S)$                                            | 27:   | return $T$                                                                                                 |

| 27:   | $C_{\ell_M-1} \gets trunc\text{-msb}(C_{\ell_M-1},  M  \bmod r)$ |       |                                                                                                            |

| 28:   | $C \leftarrow (C_0, C_1, \dots, C_{\ell_M - 1})$                 | 28: t | trunc-msb(X, n):                                                                                           |

| 29:   | $\mathbf{return}\ (S,C)$                                         | 29:   | if $n = 0$ then:                                                                                           |

|       |                                                                  | 30:   | $\mathbf{return}\;\phi$                                                                                    |

| 30: p | $pad_{r}(X)$ :                                                   | 31:   | else:                                                                                                      |

| 31:   | $X \leftarrow X    10^{r-1-( X  \mod r)}$                        | 32:   | $\mathbf{return}\;(x_0,x_1,\ldots,x_{n-1})$                                                                |

| 32:   | return X                                                         |       |                                                                                                            |

| 33: t | runc-lsb $(X, n)$ :                                              |       |                                                                                                            |

| 34:   | return $(x_{r-n}, x_{r-n+1},, x_{r-1})$                          |       |                                                                                                            |

|       |                                                                  |       |                                                                                                            |

Figure 2.3: Schematic diagram of ACE- $\mathcal{AE}$ -128 AEAD algorithm

#### 2.4.1 Rate and capacity part of state

The following 8 bytes constitute the  $S_r$  part of state and are used for both absorbing and squeezing.

$$A[7], A[6], A[5], A[4], C[7], C[6], C[5], C[4]$$

The rationale of these byte positions is explained in Section 5.8. The remaining bytes form the  $S_c$  part of state.

#### 2.4.2 Padding

Padding is necessary when the length of the processed data is not a multiple of the rate r value. Since the key size is a multiple of r, we get two key blocks  $K_0$  and  $K_1$ , so no padding is needed. Afterwards, the padding rule  $(10^*)$ , denoting a single 1 followed by the required number of 0's, is applied to the message M, so that its length after padding is a multiple of r. The resulting padded message is divided into  $\ell_M r$ -bit blocks  $M_0 \| \cdots \| M_{\ell_M - 1}$ . A similar procedure is carried out on the associated data AD which results in  $\ell_{AD} r$ -bit blocks  $AD_0 \| \cdots \| AD_{\ell_{AD} - 1}$ . In the case where no associated data is present, no processing is necessary. We summarize the padding rules for the message and associated data below.

$$\begin{aligned} \mathsf{pad}_\mathsf{r}(M) &\leftarrow M \|1\| 0^{r-1-(|M| \bmod r)} \\ \mathsf{pad}_\mathsf{r}(AD) &\leftarrow \begin{cases} AD \|1\| 0^{r-1-(|AD| \bmod r)} & \text{if } |AD| > 0 \\ \phi & \text{if } |AD| = 0 \end{cases} \end{aligned}$$

Note that in case of AD or M whose length is a multiple of r, an additional r-bit padded block is appended to AD or M to distinguish between the processing of partial and complete blocks.

#### 2.4.3 Loading key and nonce

The state is loaded byte-wise with 128-bit nonce  $N = N_0 ||N_1|$  and 128-bit key  $K = K_0 ||K_1|$ , and the remaining eight bytes are set to zero. All nonce bytes are divided and loaded in the words B and E in a descending byte order. The key is loaded in words A and C in the same manner. The word D is initialized by the zero bytes. Symbolically, the state is initialized as follows.

| $A[7], A[6], \cdots, A[0] \leftarrow K_0[7], K_0[6], \cdots, K_0[0]$ |

|----------------------------------------------------------------------|

| $C[7], C[6], \cdots, C[0] \leftarrow K_1[7], K_1[6], \cdots, K_1[0]$ |

| $B[7], B[6], \cdots, B[0] \leftarrow N_0[7], N_0[6], \cdots, N_0[0]$ |

| $E[7], E[6], \cdots, E[0] \leftarrow N_1[7], N_1[6], \cdots, N_1[0]$ |

| $D[7], D[6], \cdots, D[0] \leftarrow 0x00, 0x00, \cdots, 0x00$       |

We use load- $\mathcal{AE}(N, K)$  to denote the process of loading the state with nonce N and key K bytes in the positions described above.

#### 2.4.4 Initialization

The goal of this phase is to initialize the state S with public nonce N and secret key K. The state is first loaded using load- $\mathcal{AE}(N, K)$  as described above. Afterwards, the permutation ACE is applied to the state, and the two key blocks are absorbed into the state with ACE applied each time. The initialization steps are described below.

$$S \leftarrow \mathsf{ACE}(\mathsf{load} - \mathcal{AE}(N, K))$$

$$S \leftarrow \mathsf{ACE}(S_r \oplus K_0, S_c)$$

$$S \leftarrow \mathsf{ACE}(S_r \oplus K_1, S_c)$$

#### 2.4.5 Processing associated data

If there is associated data, each  $AD_i$  block,  $i = 0, \ldots, \ell_{AD} - 1$  is XORed with the  $S_r$  part of the internal state S, and one-bit domain separator is XORed to lsb of E[0]. Then, the ACE permutation is applied to the whole state.

$$S \leftarrow \mathsf{ACE}(S_r \oplus AD_i, S_c \oplus (0^{c-2} || 01)), \ i = 0, \dots, \ell_{AD} - 1$$

This phase is defined in Algorithm 2.

#### 2.4.6 Encryption

Similar to the processing of associated data, however, with a different domain separator, each message block  $M_i$ ,  $i = 0, \ldots, \ell_M - 1$  is XORed to the  $S_r$  part of the internal state

S resulting in the corresponding ciphertext  $C_i$ , which is extracted from the  $S_r$  part of the state. After the computation of each  $C_i$ , the whole internal state is permuted by applying ACE, i.e.,

$$C_i \leftarrow S_r \oplus M_i,$$

$$S \leftarrow \mathsf{ACE}(C_i, S_c \oplus (0^{c-2} \| 10)), \ i = 0, \cdots, \ell_M - 1$$

The last ciphertext block  $C_{\ell_M-1}$  is truncated so that its length is equal to that of the last unpadded message block. The details of encryption procedure is given in Algorithm 2.

#### 2.4.7 Finalization

After the extraction of the last ciphertext block and a single call of ACE, the domain separator is reset to 0x00 indicating the start of the finalization phase. Afterwards, the two key blocks are absorbed into the state. Finally, the tag is extracted from the same byte positions that are used for loading the key. The finalization steps are mentioned below and illustrated in Algorithm 2.

$$S \leftarrow \mathsf{ACE}(S_r \oplus K_i, S_c), \ i = 0, 1$$

$$T \leftarrow \mathsf{tagextract}(S).$$

The function tagextract(S) extracts the 128-bit tag  $T = T_0 ||T_1|$  from the state bytes as follows.

$$T_0[7], T_0[6], \cdots, T_0[0] \leftarrow A[7], A[6], \cdots, A[0]$$

$$T_1[7], T_1[6], \cdots, T_1[0] \leftarrow C[7], C[6], \cdots, C[0]$$

#### 2.4.8 Decryption

The decryption procedure is symmetrical to the encryption procedure and illustrated in Algorithm 2.

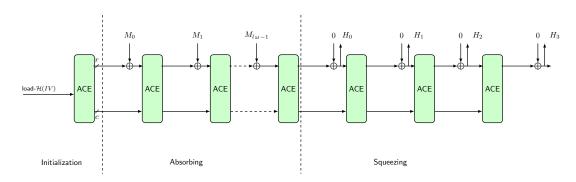

# 2.5 Hash Algorithm: ACE-H-256

The hash algorithm ACE- $\mathcal{H}$ -256 takes message M and a pre-defined initialization vector IV of length 24 bits as inputs, and then returns 256-bit message digest H. The depiction of the ACE- $\mathcal{H}$ -256 is shown in Figure 2.4 and illustrated in Algorithm 3. We now describe each phase of ACE- $\mathcal{H}$ -256 in detail.

Figure 2.4: Hash algorithm ACE-H-256

#### 2.5.1 Message padding

The padding rule (10<sup>\*</sup>) similar to ACE- $\mathcal{AE}$ -128 is applied to the input message M, where a single 1 followed by 0's is appended to it such that its length after padding is a multiple of r. We denote the padding rule by

$$pad_{r}(M) = M || 10^{r-1-(|M| \mod r)}$$

The resulting padded message is then divided into  $\ell_M$  r-bit blocks  $M_0 \| \cdots \| M_{\ell_M - 1}$ .

#### 2.5.2 Loading initialization vector

The state is first initialized by IV = h/2||r||r', where r' denotes the number of bits squeezed per permutation call (r = r' = 64 for ACE- $\mathcal{H}$ -256). Eight bits are used to encode each of the used h/2, r and r' sizes [21] and loaded in word B as follows.

$$B[7] \leftarrow 0x80$$

$$B[6] \leftarrow 0x40$$

$$B[5] \leftarrow 0x40$$

The remaining bytes are set to 0x00. We denote this process by load- $\mathcal{H}(IV)$ .

#### 2.5.3 Initialization

The load- $\mathcal{H}(IV)$  procedure loads the state with the IV. Then a single call of ACE completes the initialization phase.

$$S \leftarrow \mathsf{ACE}(\mathsf{load}\text{-}\mathcal{H}(IV))$$

#### 2.5.4 Absorbing and squeezing

Each message block is absorbed by XORing it to the  $S_r$  part of the state (see Section 2.4.1), then the ACE permutation is applied. After absorbing all the message blocks, the *h*-bit output is extracted from the  $S_r$  part of the state *r* bits at a time followed by the application of the ACE permutation until a total of 4 extractions are completed.

# Algorithm 3 ACE-H-256 algorithm

| 1: A  | CE-H-256(M, IV):                            | 1: At | osorbing(S,M):                                          |

|-------|---------------------------------------------|-------|---------------------------------------------------------|

| 2:    | $S \leftarrow Initialization(IV)$           | 2:    | $(M_0    \cdots    M_{\ell_M - 1}) \leftarrow pad_r(M)$ |

| 3:    | $S \leftarrow Absorbing(S, M)$              | 3:    | for $i = 0$ to $\ell_M - 1$ do:                         |

| 4:    | $H \leftarrow Squeezing(S)$                 | 4:    | $S \leftarrow ACE(S_r \oplus M_i, S_c)$                 |

| 5:    | return H                                    | 5:    | return S                                                |

| 6: In | itialization(IV):                           | 6: Sq | ueezing(S):                                             |

| 7:    | $S \leftarrow load-\mathcal{H}(IV)$         | 7:    | for $i = 0$ to 2 do:                                    |

| 8:    | $S \leftarrow ACE(S)$                       | 8:    | $H_i \leftarrow S_r$                                    |

| 9:    | return $S$                                  | 9:    | $S \leftarrow ACE(S)$                                   |

|       |                                             | 10:   | $H_3 \leftarrow S_r$                                    |

| 10: p | $ad_{r}(M)$ :                               | 11:   | $return H_0    H_1    H_2    H_3$                       |

| 11:   | $M \leftarrow M    10^{r-1 - ( M  \mod r)}$ |       |                                                         |

| 12:   | <b>return</b> $M$                           |       |                                                         |

|       |                                             |       |                                                         |

# Chapter 3 Security Claims

ACE is an all-in-one primitive and provides both authenticated encryption with associated data and hashing functionalities. The AEAD mode assumes a nonce respecting adversary and we do not claim any security in the event of nonce reuse. If the verification procedure fails, the decrypted ciphertext and the new tag should not be given as output. Moreover, we claim no security for reduced-round versions of ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256. In summary, the security claims of ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256 are given in Tables 3.1 and 3.2, respectively.

Note that the integrity security in Table 3.1 includes the integrity of nonce, associated data and plaintext.

| Table 3.1: | Security | goals | of ACE- | - <i>AE</i> -128 | (in | bits) |

|------------|----------|-------|---------|------------------|-----|-------|

|------------|----------|-------|---------|------------------|-----|-------|

| Confidentiality | Integrity | Authenticity | Data limit |

|-----------------|-----------|--------------|------------|

| 128             | 128       | 128          | $2^{124}$  |

Table 3.2: Security goals of ACE- $\mathcal{H}$ -256 (in bits)

| Collision | Preimage | Second preimage |

|-----------|----------|-----------------|

| 128       | 192      | 128             |

# Chapter 4 Security Analysis

In this chapter, we first analyze the security of the ACE permutation by assessing its indistinguishability properties against various distinguishing attacks. We primarily focus on the diffusion behavior, expected upper bounds on the probabilities of differential and linear characteristics, algebraic properties and self-symmetry based distinguishers. Next, we present the security bounds of ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256, whose results directly follow the security proofs of sponge modes.

In our analysis, we denote the linear layer by  $\pi$ , i.e.,  $\pi$  permutates the words of state. For example, if  $\pi(0, 1, 2, 3, 4) = (3, 2, 0, 4, 1)$ , then after applying  $\pi$ , the state A||B||C||D||E is transformed to D||C||A||E||B. Moreover, by the component function  $f_j$  we refer to the Algebraic Normal Form (ANF) of the *j*-th bit.

## 4.1 Diffusion

To assess the diffusion behavior, we evaluate the minimum value of  $u \times s$  such that each component function of the state after s steps depends on all the input state bits. We find that u = 11 gives full bit diffusion within a single Simeck sbox. Since ACE has five words that are updated in each step, we note that s has to be at least 5. Accordingly, we search for the following values of  $(u, s) \in \{(i, 5) | 1 \le i \le 11\}$ . Note that for u = 8 and s = 5, the number of linear layers satisfying the full bit diffusion property are 13, and  $\pi = (3, 2, 0, 4, 1)$  is one among them.

Given that (u, s) = (8, 16) and  $\pi = (3, 2, 0, 4, 1)$  for ACE, we claim that meet/missin-the-middle distinguishers cannot cover more than ten steps, because ten steps guarantees full bit diffusion in both forward and backward directions.

### 4.2 Differential and Linear Cryptanalysis

To analyze the security of ACE w.r.t differential and linear distinguishers [17, 28], we model ACE using Mixed Integer Linear Programming (MILP) and bound the minimum number of active Simeck sboxes (SB-64). We then provide expected bounds for the

maximum probabilities of differential (resp. linear) characteristics. Table 4.1 depicts the minimum number of active Simeck sboxes for all linear layers.

#### 4.2.1 Expected bounds on the maximum probabilities of differential and linear characteristics

Let  $n_s(\pi)$  be the minimum number of active Simeck shoxes in s steps for a linear layer  $\pi$ , and p denote the Maximum Differential Probability bound (MDP) for a u-round Simeck shox in  $\log_2(\cdot)$  scale. An in-depth analysis of values of p has been provided in [6] (cf. Section 4.2). We choose u, s and  $\pi$  such that

- the upper bound on the maximum differential characteristic probability is less than  $2^{-320}$ , i.e.,  $|n_s(\pi)p| > 320$ .

- $u \times s$  is minimum and s is at least three times the number of steps required for full bit diffusion. This implies  $s \ge 15$  for ACE.

For (u, s) = (8, 16) and  $\pi = (3, 2, 0, 4, 1)$ ,  $n_s(\pi) = 21$  and p = -15.8. Thus,  $|21 \times (-15.8)| \approx 331.8 > 320$  and maximum differential characteristic probability bound is  $2^{-331.8}$ . The maximum squared correlation of a linear characteristic is computed analogously using  $\gamma = -15.6$  and equals  $2^{-327.6}$ , where  $\gamma$  is the maximum square correlation of a 8-round Simeck sbox (cf. Section 4.2.2 [6]).

### 4.3 Algebraic Properties

In this section, we provide bounds for the algebraic degree of ACE and evaluate its security against integral distinguishers. We use the bit based division property [29, 9] to compute the algebraic degree. We find that the algebraic degree of a 8-round Simeck sbox is 36. Note that the algebraic degree (after 8 rounds) of all component functions from  $f_0 - f_{31}$  is 36 while it is 27 for the component functions  $f_{32} - f_{63}$ . Thus, to evaluate the algebraic degree of ACE it is enough to find bounds for algebraic degree of the component functions  $f_0, f_{32}, f_{64}, f_{96}, f_{128}, f_{160}, f_{192}, f_{224}, f_{256}$  and  $f_{288}$ . Table 4.2 provides bounds of the algebraic degree for the above component functions.

Note that since the number of words in ACE is odd, due to slow diffusion the algebraic degrees are 63 and 62 for the component functions  $f_{64}$  and  $f_{96}$  after 2 steps, respectively. A similar trend can be seen for the component functions  $f_{256}$  and  $f_{288}$ . This non-uniformity in degree continues till step five, after which the degree is stabilized to 304-313 due to full bit diffusion (Section 4.1). We expect that the degree reaches 319 in six steps.

Integral distinguishers [24]. To search for the longest length integral distinguisher, we set a single bit of the input state as constant (0) and the rest are set to active (1). We then evaluate the algebraic degree at the *s*-th step of each component function in terms

| Linear layer                       |                                        |                                       |               |               |               |                |               |               | ste            | р <i>ѕ</i>     |                                        |                 |                 |                 |                 |                 |

|------------------------------------|----------------------------------------|---------------------------------------|---------------|---------------|---------------|----------------|---------------|---------------|----------------|----------------|----------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| $\pi$                              | 1                                      | 2                                     | 3             | 4             | 5             | 6              | 7             | 8             | 9              | 10             | 11                                     | 12              | 13              | 14              | 15              | 16              |

| (1, 0, 3, 4, 2)                    | 0                                      | 1                                     | 1             | 2             | 2             | 3              | 3             | 4             | 4              | 5              | 5                                      | 6               | 6               | 7               | 7               | 8               |

| (1, 0, 4, 2, 3)                    | 0                                      | 1                                     | 1             | 2             | 2             | 3              | 3             | 4             | 4              | 5              | 5                                      | 6               | 6               | 7               | 7               | 8               |

| (1, 2, 0, 4, 3)                    | 0                                      | 1                                     | 2             | 3             | 4             | 6              | 8             | 8             | 9              | 10             | 11                                     | 12              | 14              | 16              | 16              | 17              |

| (1, 2, 3, 4, 0)                    | 0                                      | 1                                     | 2             | 3             | 4             | 6              | 7             | 8             | 9              | 10             | 11                                     | 12              | 13              | 14              | 15              | 16              |

| (1, 2, 4, 0, 3)                    | 0                                      | 1                                     | 1             | 2             | 3             | 5              | 7             | 8             | 9              | 9              | 10                                     | 11              | 13              | 15              | 16              | 17              |

| (1, 3, 0, 4, 2)                    | 0                                      | 0                                     | 1             | 2             | 4             | 4              | 5             | 7             | 9              | 12             | 13                                     | 14              | 15              | 16              | 17              | 19              |

| (1, 3, 4, 0, 2)                    | 0                                      | 0                                     | 1             | 1             | 1             | 2              | 2             | 2             | 3              | 3              | 3                                      | 4               | 4               | 4               | 5               | 5               |

| (1, 3, 4, 2, 0)                    | 0                                      | 0                                     | 1             | 2             | 3             | 4              | 5             | 6             | 7              | 9              | 11                                     | 12              | 12              | 13              | 14              | 15              |

| (1, 4, 0, 2, 3)                    | $\begin{bmatrix} 0\\ 0 \end{bmatrix}$  | 1                                     | 2             | 3             | 4             | 6              | 8             | 8             | 9              | 10             | 11                                     | 12              | 14              | 16              | 16              | 17              |

| (1, 4, 3, 0, 2)                    | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$ | 1                                     | 1             | 2             | 4             | 5              | 6             | 7             | 9              | 10             | 11                                     | 12              | 14              | 15              | 16              | 18              |

| (1, 4, 3, 2, 0)                    | $\begin{bmatrix} 0\\ 0 \end{bmatrix}$  | 1                                     | 2             | 3             | 5             | 6<br>C         | 7             | 9             | 11             | 12             | 13                                     | 14              | 15              | 17              | 18              | 19<br>17        |

| (2, 0, 1, 4, 3)                    | $\begin{bmatrix} 0\\ 0 \end{bmatrix}$  | 1                                     | 2             | 3             | 4             | 6              | 67            | 8             | 9              | 10             | 11                                     | 12              | 14              | 15              | 16<br>15        | 17              |

| (2, 0, 3, 4, 1)<br>(2, 0, 4, 1, 2) |                                        | 1                                     | $\frac{2}{1}$ | $\frac{3}{2}$ | $\frac{4}{3}$ | $\frac{5}{3}$  | 7             | $\frac{8}{5}$ | $9 \\ 7$       | 10<br>0        | 11<br>10                               | 12<br>11        | $\frac{13}{12}$ | $\frac{14}{12}$ | $\frac{15}{13}$ | $\frac{16}{14}$ |

| (2, 0, 4, 1, 3) (2, 3, 0, 4, 1)    | $\begin{vmatrix} 0\\0 \end{vmatrix}$   | $\begin{array}{c} 0 \\ 0 \end{array}$ | 1<br>1        | 2<br>2        | 3<br>3        | 3<br>5         | $\frac{4}{7}$ | э<br>9        | (<br>10        | $\frac{9}{10}$ | $\begin{array}{c} 10\\ 11 \end{array}$ | $\frac{11}{12}$ | 12<br>13        | $12 \\ 15$      | $13 \\ 17$      | 14<br>19        |

| (2, 3, 0, 4, 1)<br>(2, 3, 1, 4, 0) | 0                                      | 0                                     | 1             | $\frac{2}{3}$ | 3<br>4        | 5<br>6         | $\frac{7}{7}$ | 9<br>8        | 8              | 10<br>9        | 11<br>11                               | $12 \\ 12$      | $13 \\ 13$      | 15<br>14        | $17 \\ 15$      | 19<br>16        |

| (2, 3, 4, 0)<br>(2, 3, 4, 0, 1)    | 0                                      | 0                                     | 1             | $\frac{3}{2}$ | 3             | 4              | 5             | 6             | 8<br>7         | 8              | 9                                      | 12              | 11              | $14 \\ 12$      | 13              | 10<br>14        |

| (2, 3, 4, 0, 1)<br>(2, 3, 4, 1, 0) | 0                                      | 0                                     | 0             | $\frac{2}{0}$ | 0             | 4<br>0         | $\frac{1}{0}$ | 0             | 0              | 0              | 9<br>0                                 | 0               | 0               | 0               | 0               | 0               |

| (2, 3, 4, 1, 0)<br>(2, 4, 0, 1, 3) | 0                                      | 0                                     | 1             | 3             | 4             | 5              | $\frac{1}{7}$ | 9             | 10             | 10             | 11                                     | 13              | 0<br>14         | 15              | 17              | 19              |

| (2, 4, 0, 1, 3)<br>(2, 4, 1, 0, 3) | 0                                      | 1                                     | $\frac{1}{2}$ | 3             | 4             | 5              | 7             | 8             | 9              | 10             | 11                                     | $13 \\ 12$      | 13              | $15 \\ 15$      | 16              | $13 \\ 17$      |

| (2, 4, 1, 0, 3)<br>(2, 4, 3, 0, 1) | 0                                      | 1                                     | $\frac{2}{2}$ | 3             | 5             | 5              | 6             | 7             | 8              | 10             | 10                                     | 11              | $10 \\ 12$      | 13              | 15              | $15^{11}$       |

| (2, 4, 3, 1, 0)                    | 0                                      | 0                                     | 1             | 2             | 4             | 6              | 7             | 8             | 9              | 10             | 11                                     | 11              | 13              | 14              | 15              | 16              |

| (2, 1, 0, 1, 0)<br>(3, 0, 1, 4, 2) | 0                                      | 1                                     | 1             | 2             | 4             | 6              | 8             | 8             | 10             | 10             | 11                                     | 13              | 15              | 16              | 17              | 19              |

| (3, 0, 4, 1, 2)                    | 0                                      | 0                                     | 1             | 1             | 1             | 2              | 2             | 2             | 3              | 3              | 3                                      | 4               | 4               | 4               | 5               | 5               |

| (3, 0, 4, 2, 1)                    | 0                                      | 1                                     | 1             | 2             | 3             | 4              | 5             | 6             | 7              | 8              | 9                                      | 10              | 11              | 12              | 13              | 14              |

| (3, 2, 0, 4, 1)                    | 0                                      | 1                                     | 2             | 3             | 5             | $\overline{7}$ | 8             | 9             | 11             | 12             | 13                                     | 15              | 16              | 17              | 19              | <b>21</b>       |

| (3, 2, 1, 4, 0)                    | 0                                      | 1                                     | 2             | 2             | 3             | 4              | 4             | 5             | 6              | 6              | 7                                      | 8               | 8               | 9               | 10              | 10              |

| (3, 2, 4, 0, 1)                    | 0                                      | 1                                     | 1             | 2             | 2             | 3              | 3             | 4             | 4              | 5              | 5                                      | 6               | 6               | 7               | $\overline{7}$  | 8               |

| (3, 2, 4, 1, 0)                    | 0                                      | 0                                     | 1             | 2             | 3             | 6              | 8             | 9             | 9              | 10             | 11                                     | 12              | 15              | 16              | 18              | 18              |

| (3, 4, 0, 1, 2)                    | 0                                      | 0                                     | 1             | 2             | 3             | 4              | 5             | 6             | $\overline{7}$ | 8              | 9                                      | 10              | 11              | 12              | 13              | 14              |

| (3, 4, 0, 2, 1)                    | 0                                      | 1                                     | 2             | 3             | 4             | 4              | 5             | 6             | 7              | 8              | 8                                      | 9               | 10              | 11              | 12              | 12              |

| (3, 4, 1, 0, 2)                    | 0                                      | 1                                     | 1             | 2             | 2             | 3              | 3             | 4             | 4              | 5              | 5                                      | 6               | 6               | $\overline{7}$  | $\overline{7}$  | 8               |

| (3, 4, 1, 2, 0)                    | 0                                      | 1                                     | 2             | 3             | 5             | 7              | 8             | 9             | 11             | 12             | 13                                     | 15              | 16              | 17              | 19              | 21              |

| (4, 0, 1, 2, 3)                    | 0                                      | 1                                     | 2             | 3             | 4             | 5              | 7             | 8             | 10             | 12             | 13                                     | 13              | 14              | 15              | 17              | 19              |

| (4, 0, 3, 1, 2)                    | 0                                      | 0                                     | 1             | 2             | 3             | 3              | 4             | 5             | 7              | 9              | 10                                     | 11              | 12              | 12              | 13              | 14              |

| (4, 0, 3, 2, 1)                    | 0                                      | 1                                     | 2             | 3             | 4             | 5              | 6             | 8             | 10             | 11             | 12                                     | 13              | 14              | 15              | 16              | 17              |

| (4, 2, 0, 1, 3)                    | 0                                      | 0                                     | 1             | 2             | 4             | 6              | 7             | 9             | 10             | 11             | 12                                     | 13              | 14              | 15              | 17              | 19              |

| (4, 2, 1, 0, 3)                    | 0                                      | 1                                     | 2             | 2             | 3             | 4              | 4             | 5             | 6              | 6              | 7                                      | 8               | 8               | 9               | 10              | 10              |

| (4, 2, 3, 0, 1)                    | 0                                      | 1                                     | 2             | 3             | 5             | 6              | 8             | 9             | 10             | 11             | 12                                     | 14              | 16              | 17              | 18              | 19              |

| (4, 2, 3, 1, 0)                    | 0                                      | 0                                     | 1             | 1             | 2             | 3              | 4             | 4             | 4              | 5              | 5                                      | 6               | 7               | 8               | 8               | 8               |

| (4, 3, 0, 1, 2)                    | 0                                      | 0                                     | 0             | 0             | 0             | 0              | 0             | 0             | 0              | 0              | 0                                      | 0               | 0               | 0               | 0               | 0               |

| (4, 3, 0, 2, 1)                    | 0                                      | 0                                     | 1             | 2             | 3             | 5              | 6             | 7             | 10             | 10             | 11                                     | 12              | 13              | 15              | 16              | 17              |

| (4, 3, 1, 0, 2)                    | 0                                      | 0                                     | 1             | 2             | 4             | 5              | 6             | 7             | 9              | 10             | 11                                     | 12              | 13              | 14              | 15              | 17              |

| (4, 3, 1, 2, 0)                    | 0                                      | 0                                     | 1             | 1             | 2             | 3              | 4             | 4             | 4              | 5              | 5                                      | 6               | 7               | 8               | 8               | 8               |

Table 4.1: Minimum number of active Simeck sboxes for s-step ACE

|     |        |         | Component function |           |           |           |           |           |           |           |           |

|-----|--------|---------|--------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| ste | eps(s) | $f_0$   | $f_{32}$           | $f_{64}$  | $f_{96}$  | $f_{128}$ | $f_{160}$ | $f_{192}$ | $f_{224}$ | $f_{256}$ | $f_{288}$ |

|     | 1      | 36      | 27                 | 36        | 27        | 36        | 27        | 36        | 27        | 36        | 27        |

|     | 2      | 92      | 83                 | 63        | 62        | 92        | 83        | 92        | 83        | 63        | 62        |

|     | 3      | 126     | 125                | 119       | 117 - 120 | 239-247   | 235 - 245 | 236-249   | 233 - 248 | 119       | 118-120   |

|     | 4      | 240-247 | 238-246            | 241 - 248 | 242 - 247 | 306-312   | 303 - 311 | 304 - 313 | 304 - 311 | 241 - 248 | 241 - 247 |

Table 4.2: Bounds on the algebraic degree of ACE

of the involved active bits. If the algebraic degree equals the number of active bits, then the bit is unknown (i.e., XOR sum of the component function is unpredictable). Otherwise, it is balanced in which case the XOR sum is always zero.

In Table 4.3, we list the integral distinguishers of ACE. Note that the positions of constant bits are chosen based on the degree of the Simeck sbox.

| Steps $s$ | Input division property | Balanced bits   |

|-----------|-------------------------|-----------------|

|           | $1^{32}  0  1^{287}$    | 64-127, 256-319 |

|           | $1^{96}  0  1^{223}$    | None            |

| 8         | $1^{160}  0  1^{159}$   | None            |

|           | $1^{224}  0  1^{95}$    | 64-127, 256-319 |

|           | $1^{288}  0  1^{31}$    | None            |

Table 4.3: Integral distinguishers of ACE

## 4.4 Self Symmetry-based Distinguishers

A cryptographic permutation is vulnerable to attacks such as rotational distinguishers, slide distinguishers [18] and invariant subspace attack [26] which exploit the symmetric properties of a round function. For example, in ACE the nonlinear Simeck sbox is rotational invariant if constants are not added at each round. Thus, a proper choice of round constants is required to mitigate the above attacks.

ACE employs an 7-bit LFSR to generate round and step constants (see Section 5.6.2). Below we list properties of the constants which ensure that each step function of ACE is distinct.

- For  $0 \le i \le 15$ ,  $sc_0^i \ne sc_1^i \ne sc_2^i$

- For  $0 \le i \le 15$ ,  $(rc_0^i, rc_1^i, rc_2^i) \ne (sc_0^i, sc_1^i, sc_2^i)$

- For  $0 \le i, j \le 15$  and  $i \ne j, (rc_0^i, rc_1^i, rc_2^i) \ne (rc_0^j, rc_1^j, rc_2^j)$

- For  $0 \le i, j \le 15$  and  $i \ne j$ ,  $(sc_0^i, sc_1^i, sc_2^i) \ne (sc_0^j, sc_1^j, sc_2^j)$ .

# 4.5 Security of ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256

The security proofs of modes based on the sponge construction rely on the indistinguishability of the underlying permutation from a random one [11, 15, 14, 22]. In previous sections, we have shown that there are no distinguishers for 16 steps of ACE. Thus, the security bounds of sponge modes are applicable to both ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256.

**ACE-** $\mathcal{AE}$ **-128 security**. We assume a nonce-respecting adversary, i.e, for a fixed K, the nonce N is never repeated. Then considering a data limit of  $2^d$ , k-bit security is achieved if  $c \ge k + d + 1$  and  $d \ll c/2$  [14]. The parameter set of ACE- $\mathcal{AE}$ -128 (Table 2.1 in Section 2.2) with actual effective capacity 254 (2 bits are lost for domain separation) satisfies this condition, and hence ACE- $\mathcal{AE}$ -128 provides 128-bit security for confidentiality, integrity and authenticity.

Note that we could use r = 192, d = 64 and obtain the same level of security [22]. However, this would require an additional 128 XORs and cannot meet our objective to achieve both AEAD and hash functionalities using the same hardware circuit. Nevertheless, this is another option for ACE with high throughput.

**ACE-** $\mathcal{H}$ **-256** security. For a sponge based hash with b = r + c and *h*-bit message digest, the generic security bounds [13, 21] are given by:

- Collision:  $\min(2^{h/2}, 2^{c/2})$

- Preimage:  $\min(2^{\min(h,b)}, \max(2^{\min(h,b)-r}, 2^{c/2}))$

- Second-preimage:  $\min(2^h, 2^{c/2})$

Accordingly, ACE-H-256 provides 128, 192 and 128-bit securities for collision, preimage and second preimage, respectively.

# Chapter 5 Design Rationale

In this chapter, we provide the rationale for our design choices and justify the design principles of each component of ACE, ACE- $\mathcal{AE}$ -128 and ACE- $\mathcal{H}$ -256.

# 5.1 Choice of the Mode: sLiSCP Sponge Mode

Our adopted mode is a variation of the sponge duplex construction. Sponge constructions are very diversified in terms of the offered security level. Particularly, it is proven that the sponge and its single pass duplex mode offer a  $2^{c/2}$  bound against generic attacks [12, 15] which provides a lower bound on the width of the underlying permutation. However, for authenticated encryption (AE), a security level of  $2^{c-d}$  is proven when the number of queries is upper bounded by  $2^d$  [16]. When restricting the data complexity to the maximum of  $2^d$  queries with  $d \ll c/2$ , one can reduce the capacity and increase the rate for a better throughput with the same security level. Jovanovic *et.al.* [22] have shown that sponge based AE achieve higher security bound, i.e., min $\{2^{b/2}, 2^c, 2^k\}$ compared to [14]. However, we are concerned with the former bound, as shown in Section 4.5.

In sponge keyed encryption modes, nonce reuse enables the encryption of two different messages with the same key stream, which undermines the privacy of the primitive. More precisely, the sponge duplex authenticated encryption mode requires the uniqueness of a nonce when encrypting different messages with the same key because the ability of the attacker to acquire multiple combinations of input and output differences leaks information about the inner state bits, which may lead to the reconstruction of the full state [15, 10]. Nonce reuse in the duplex constructions reveals the XOR difference between the first two plaintexts by XORing their corresponding ciphertexts. On the other hand, a nonce reuse differential attack may be exploited if the attacker is able to inject a difference in the plaintext and cancel it out by another difference after the permutation application. However, such an attack depends on the probability of the best differential characteristic and the number of rounds of the underlying permutation. Accordingly, if such a permutation offers enough resistance to differential cryptanalysis, the feasibility of nonce reuse differential attacks is minimal. The condition on the differential behavior of the underlying permutation is also important when considering resynchronization attacks, where related nonces are to be used. For that reason, even if nonce reuse is not permitted, the underlying permutation used in the initialization stage should be strong enough to mitigate differential attacks.

Given the above results, the sLiSCP sponge mode [5] realizes the following objectives:

- The flexibility to adapt the same circuitry to provide both authenticated encryption and hashing functionalities, as we adopt a unified round function for all functionalities.

- High key agility, which fits the lightweight requirements, because AE mode require no key scheduling.

- Simplicity, as there is no need to implement a decryption algorithm, because the same encryption algorithm is used for decryption.

- Both plaintext and ciphertext blocks are generated online without the need to process the whole input message and encrypted material first.

- Keyed initialization and finalization phases that make key recovery hard even if the internal state is recovered and also renders universal forgery with the knowledge of the internal state unattainable.

- Hardware efficient initialization and finalization stages where the state is initialized with the key which is again absorbed in the rate part afterward.