Design team members: Mark Wilkinson

Supervisors: Kevin Law

Background

Financial markets are constantly adapting to new technologies becoming faster, smarter and more efficient. Automatic trading allows for a computer system to act on market information within microseconds, sending and modifying tens of thousands of orders in second [1]. As most exchanges execute orders on a time-price priority, a digital arms race has developed amongst competing high-frequency firms, with slower systems at the complete mercy of the fastest system. In order to push the envelope of high-frequency, low-latency trading further it is now necessary to overcome the limitations of traditional computer architecture through hardware acceleration.

Traditionally, optimizing code at the application level was sufficient in order to reduce latencies in the millisecond order of magnitude. However, now that trading times have been lowered into microseconds [2] it is no longer sufficient to mealy optimise application level code, as the inefficiencies found in traditional computer architecture limit the latency achievable by this approach. A number of products and technologies exist which work to overcome many of the latency bottlenecks found in traditional systems, however, as processing still needs to be done at the application level they are unable to achieve the theoretical low latencies possible on FPGA based designs [3].

Investment Technology Group, Inc. (ITG) an industry leader in electronic trading has sponsored this project, providing industry knowledge and resources.

Project description

The overall objective of this project is to, design and implement a hardware accelerated equity trading system optimized for running a cross market strategy. In order to be successful the trading system will need to meet the primary objectives outlined below.

- Ultra Low Latency

- Financial Information eXchange Protocol 4.2 Compliant [4]

- Level One Quote Support

- Implement Cross-Market Strategy

Design methodology

Hardware Selection – Various hardware devices were investigated and analysed with a NetFPGA device proving optimal based on a number of constraints. The NetFPGA allows for gigabit Ethernet connectivity, real-time communication with software and provides a useable framework.

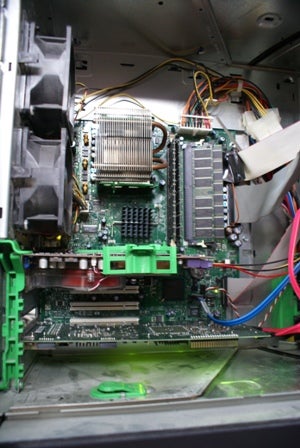

NetFPGA (Bottom card) In Prototype Computer

Network

Communication

–

Successfully

establishing

network

communication

through

the

NetFPGA

is

a

major

milestone

towards

accomplishing

the

objectives

of

this

project.

How

network

communication

is

handled

through

the

FPGA

will

help

to

realise

the

limitations

of

the

NetFPGA

hardware

and

also

shape

the

final

solution

and

prototype.

Trade

System

Integration

-

Once

communication

has

been

established

between

the

application

level,

NetFPGA

and

an

external

test

computer

a

trade

system

can

be

built

onto

this

framework.

The

limitations

discovered

of

the

NetFPGA

hardware

in

how

communication

needs

to

be

handled

will

drastically

influence

how

the

trading

system

is

integrated

and

what

aspects

of

processing

are

handled

on

the

FPGA

and

what

remains

in

software.

The

trading

system

can

be

broken

down

into

two

parts,

the

first

dealing

with

external

communication,

the

FIX

and

quote

engines

and

the

second

the

internal

trading

logic.

Low-Latency

Adjustments

–

In

order

to

achieve

the

desired

low

latency,

a

number

of

unconventional

theoretical

techniques

have

been

drafted

which

will

need

to

be

implemented

and

refined.

More Information

For more information please attend the Systems Design Engineering Design Symposium.

- Solace Systems. Trading microseconds for nanoseconds. September 23, 2009. Accessed November 2010. https://solace.com/blog/trading-microseconds-for-nanoseconds/

- BATS Trading. BATS System Performance. Accessed November2010. http://batstrading.com/resources/features/bats_exchange_Latency.pdf

- in-FPGA Trading Systems. Trade Response Latency Reduced to Under Two Microseconds by Combining NASDAQ ITCH and OUCH into a Single FPGA. September 14, 2010. Accessed November 2010.