Background

SET and RESET operations are fundamental operations in Resistive Random Access Memory (RRAM). Most techniques for programming RRAM-based Compute In Memory (CIM) cells use an iterative write-verify algorithm. However, given the state-of-the-art AI models often have over 100 million parameters, simply increasing the memory size leads to yield issues and prolonged programming times due to significant write variations in RRAM cells. To address this, optimizing the conventional write-verify algorithm for multi-level programming is crucial.

Description of the invention

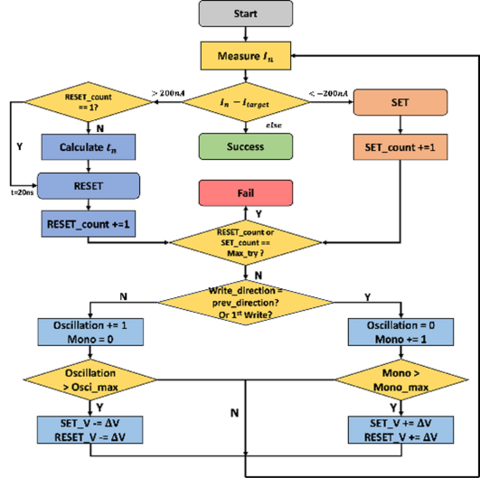

Researchers at the University of Waterloo have developed a state aware write-verify algorithm based on the transient characteristics of RESET behavior which significantly reduces the average write time. Using a feedback mechanism, the algorithm predicts and tunes parameters for multi-level programming of RRAMs. Instead of pulse strengths, the algorithm utilizes pulse length to tune the states (write bits) in multi-level/multi-bit RRAM cells hence significantly increases the average write operation speed. The algorithm was successfully tested in programming of the in-house fabricated multi-level TiN/TiOx/TiN resistive switching RRAM cells.

Advantages

- Faster and more accurate writing: testing the developed algorithm in programming multi-level RRAMs showed that the average write time is reduced by >70 percent compared to the conventional write-verify algorithms and retains better state margins.

- Widely applicable: the algorithm is potentially applicable to all resistive random access memory cells.

- 10+ states programing for RRAMs.

- Directly applicable to commercial-grade devices.

- RESET termination minimized variability of write operations for RRAMs

Potential applications

The algorithm is applicable to multi-bit RRAMs used in:

- Compute In Memory (CIM): parallel processing & energy efficiency

- High Density Data Storage.

- Artificial Intelligence and Machine Learning: on-chip learning & neural network acceleration

- Flexible and Wearable electronics

Flow-chart of the write-verify algorithm for multi-bit encoding

Reference

10262

Patent status

Patent pending

Stage of development

Prototype tested

Ongoing research

Contact

Scott Inwood

Director of Commercialization

Waterloo Commercialization Office

sinwood@uwaterloo.ca

uwaterloo.ca/research